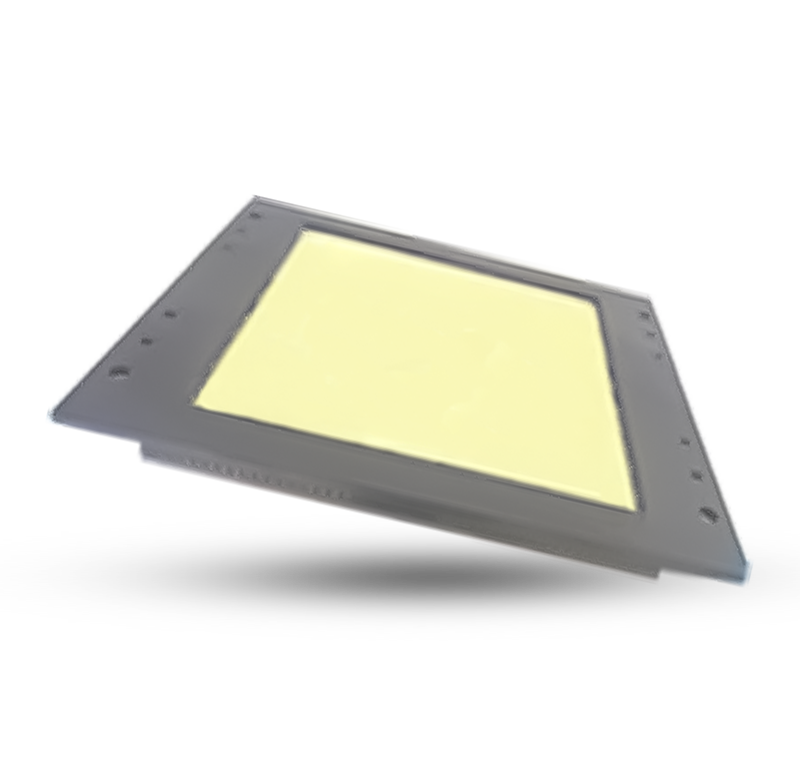

セラミックPGAパッケージ(CPGA)

-

製品の説明

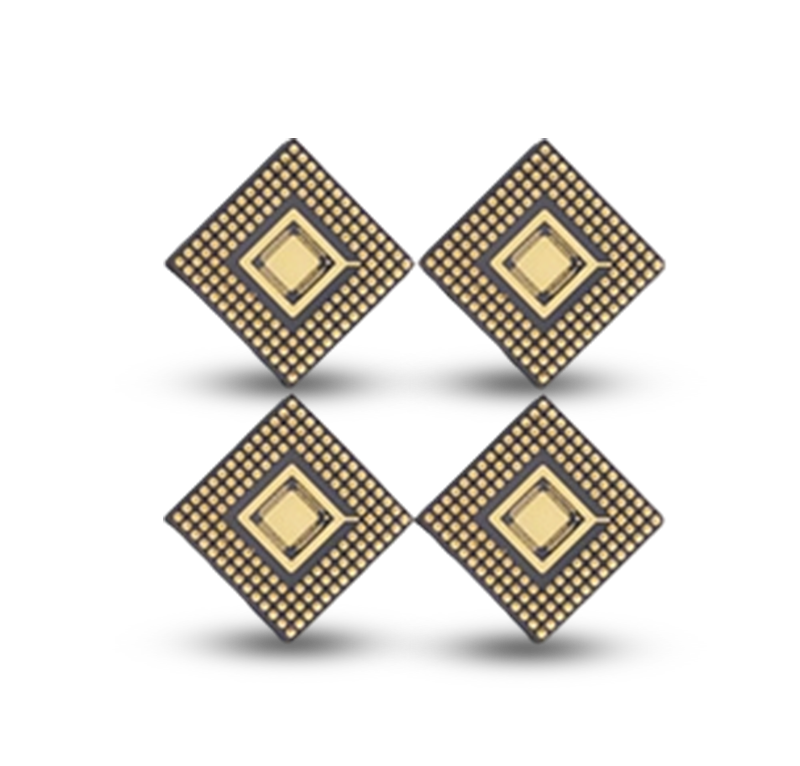

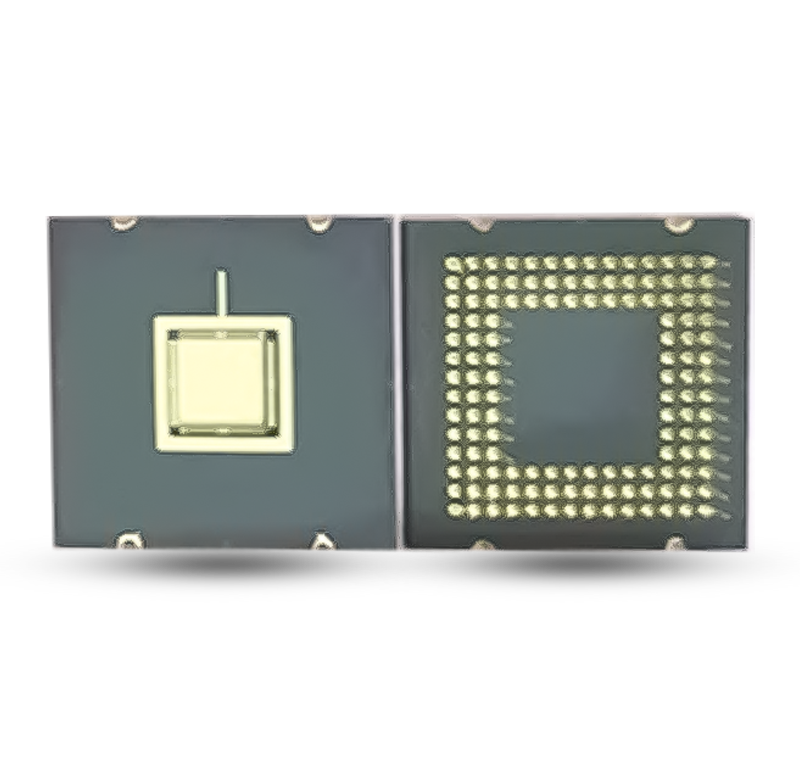

CPGA(Ceramic Pin Grid Array)パッケージは、VLSIで一般的に用いられる挿入実装(スルーホール実装)タイプのパッケージです。高密度実装に対応し、電気的・熱的特性に優れるとともに、気密性・信頼性にも優れています。 ピンピッチは主に 2.54mm で、規則配列およびスタガ(千鳥)配列に対応します。構造は キャビティアップ と キャビティダウン の2種類があり、キャビティダウン構造はパッケージ背面にヒートシンクを取り付けやすく、放熱性能の向上に有利です。一方、キャビティアップ構造はキャビティ寸法を大きく確保できるため、大型チップやマルチチップの実装に適しています。 CPGAパッケージは、CPU、DSP、CCD、ASIC などの VLSI チップの封止・パッケージ用途に広く使用されています。

-

対応材料

-

応用分野

主な特性

優れた電磁シールド性能

長期気密安定性に優れる

マルチチップ集積(MCM)に対応

耐放射線性・耐高温性に優れる

優れた耐食性

高い耐湿性

熱特性と機械特性を両立した設計(熱‐機械協調設計)

ソケット実装における挿抜互換性に優れる

材料特性テーブル

|

型番 |

セラミック外形寸法 |

リードピッチ |

シールリング寸法 |

キャビティ寸法 |

総厚 |

|

G15-01 |

21.5×19.00 |

2.54 |

21.50×19.00 |

5.00×5.00 |

2.20 |

* このデータはラボでのテスト結果の一例です。特定の製造プロセスでの実際の特性とは異なる場合があります。